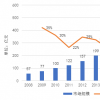

SK海力士正在围绕DDR5制定重大计划,其中包括一项前所未有的努力,将标准的时钟速度提升到远高于我们通常在单RAM代中看到的水平。目前,双通道DDR4-3200解决方案提供高达51.7GB/s的内存带宽。一个双通道DDR5-8400解决方案将把这一速度提高到每秒134.4GB/s的RAM。

为了达到这些高度,与DDR4相比,需要对DDR5进行一些更改,Hynix已经发布了关于如何计划实现这些目标的信息。

其中许多都是DDR4中功能的扩展,这并不奇怪。DDR5在8组中使用了32个银行,而DDR4在4组中使用了16个银行,并且将突发长度增加了一倍(从8个增加到16个)。其他特性是新的(或作为基线功能的新特性)。

ECC(纠错码)并不是一个新的DRAM特性,但这是我们第一次看到强制的on-dieECC内置于消费RAM标准中。

另一个应该提高整体吞吐量的优点是名为SameBankRefresh的功能(出于我不知道的原因,缩写为REFsb)。以前,DRAM刷新周期是同时针对每个DRAM银行的,在刷新周期中不能处理读/写命令。根据这一微米白皮书,所有银行刷新发布平均每3.9µs耗费295ns完成。

相同的银行刷新仅要求每个银行组中的一个银行处于空闲状态,以便命令进行处理。其他12家银行不必闲置,可以继续正常运营。每1.95µsREFsb命令发布但在130年完成ns。使用REFsb将对空闲延迟的影响从11.2ns减少到5ns。减少延迟的技巧通常比提高吞吐量要困难得多,所以几乎在每个方面都有所帮助。

根据Micron的说法,REFsb根据测试中读写的混合来提高6-9%的吞吐量。即使在相同的频率下,DDR5也应该比DDR4具有更高的吞吐量,不过显然差别并不大。

与DDR4相比,DDR5的工作电压也降低了,降至1.1v,尽管狂热爱好者喜欢的更高的时钟速度无疑会比标准模块消耗更多的能量(特别是如果Hynix实现了DDR5-8400的承诺)。

至于什么时候你应该买一个DDR5系统?这就不那么清楚了。AMD将坚持AM4和DDR4到2020年,而DDR5的产量仍在增加。我们可能会在2021年看到DDR5,但这并不是前所未有的,因为它的推出将会推迟到2022年——英特尔和AMD过去已经推迟采用RAM标准,如果价格目标或整体产品需求没有得到满足的话。

新经网

新经网